VLSI

The Process/Technology Nodes

- - Design Solutions from Specifications to GDSII sign-off for Analog, Digital and Mixed Signal chips, across process nodes from 350nm to most advanced 5nm

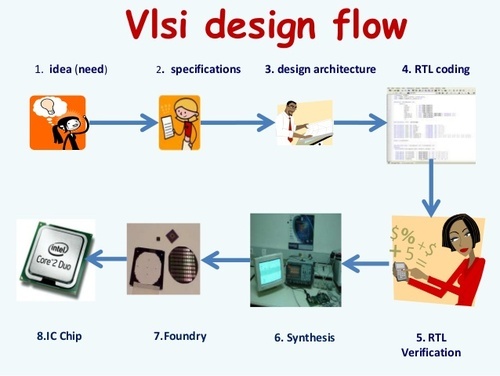

- - Digital Design Turnkey Capabilities – RTL, DV, DFT, PD, till GDS sign off

- - Analog/AMS Design Turnkey Capabilities – Analog Modelling, Circuit Design, Layout Design, AMS Verification

- - Domain experience includes Data Converters, Power Management, High Speed Interfaces – PCIe, DDR, SerDes, SAS/SATA, Ethernet, MIPI, Foundation IPs etc

- - Applications include Servers, Automotive, Graphics, Mobile platforms, Medical, Consumer products etc

- - Expertise in Pre-silicon verification, FPGA Prototyping and Emulation

- - Expertise in Post-silicon validation on Bench Char and ATE

- - Expertise in Low power, High Power, High Speed designs with the knowledge and experience in power savings and design optimisation techniques